## **Chapter 19: Translation Lookaside Buffer**

Adam Disney

#### **Crux: How To Speed Up Address Translation**

THE CRUX: HOW TO SPEED UP ADDRESS TRANSLATION How can we speed up address translation, and generally avoid the extra memory reference that paging seems to require? What hardware support is required? What OS involvement is needed?

## Overview

- Let's add a hardware cache specifically for the page tables called a Translation Lookaside Buffer (TLB).

- Sidenote:

- Caching is a fundamental performance technique used throughout computer systems to make "the common case" fast.

- Take advantage of locality (temporal and spatial)

## Overview

| 1  | <pre>VPN = (VirtualAddress &amp; VPN_MASK) &gt;&gt; SHIFT</pre> |

|----|-----------------------------------------------------------------|

| 2  | (Success, TlbEntry) = TLB_Lookup(VPN)                           |

| 3  | if (Success == True) // TLB Hit                                 |

| 4  | if (CanAccess(TlbEntry.ProtectBits) == True)                    |

| 5  | Offset = VirtualAddress & OFFSET_MASK                           |

| 6  | PhysAddr = (TlbEntry.PFN << SHIFT)   Offset                     |

| 7  | Register = AccessMemory(PhysAddr)                               |

| 8  | else                                                            |

| 9  | RaiseException (PROTECTION_FAULT)                               |

| 10 | else // TLB Miss                                                |

| 11 | PTEAddr = PTBR + (VPN * sizeof(PTE))                            |

| 12 | PTE = AccessMemory (PTEAddr)                                    |

| 13 | if (PTE.Valid == False)                                         |

| 14 | RaiseException(SEGMENTATION_FAULT)                              |

| 15 | else if (CanAccess(PTE.ProtectBits) == False)                   |

| 16 | RaiseException (PROTECTION_FAULT)                               |

| 17 | else                                                            |

| 18 | <pre>TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)</pre>            |

| 19 | RetryInstruction()                                              |

|    |                                                                 |

Figure 19.1: TLB Control Flow Algorithm

## **Example: Accessing An Array**

#### Assumptions

- Array "a" is at virtual address 100

- 8-bit virtual address space

- 16 byte pages thus 4-bit VPN and 4-bit offset

- Only "a" generates memory accesses (for simplicity)

#### Example: Accessing An Array

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                   |          |     |            | Of   | fset |         |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|------------|------|------|---------|----|

| /PN = 01<br>/PN = 02<br>/PN = 03<br>/PN = 04<br>/PN = 05<br>/PN = 06<br>/PN = 07<br>/PN = 07<br>/PN = 07<br>/PN = 07<br>/PN = 08<br>/PN = 09<br>/PN = 10<br>/PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                            | 0        | 0   | 04         | - (  | 08   | 12      | 16 |

| <pre>/PN = 02<br/>/PN = 03<br/>/PN = 04<br/>/PN = 05<br/>/PN = 05<br/>/PN = 06<br/>/PN = 07<br/>/PN = 07<br/>/PN = 07<br/>/PN = 07<br/>/PN = 08<br/>/PN = 09<br/>/PN = 10<br/>/PN = 11<br/>/PN = 12<br/>/PN = 13<br/>/PN = 14</pre>                                                                                                                     | /PN = 00 |     |            |      |      |         |    |

| /PN = 03<br>/PN = 04<br>/PN = 05<br>/PN = 06<br>/PN = 07<br>/PN = 07<br>/PN = 07<br>/PN = 08<br>/PN = 08<br>/PN = 09<br>/PN = 10<br>/PN = 11<br>/PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                                        | /PN = 01 |     |            |      |      |         |    |

| <pre>/PN = 04<br/>/PN = 05<br/>/PN = 06<br/>/PN = 07<br/>/PN = 07<br/>/PN = 07<br/>/PN = 08<br/>/PN = 08<br/>/PN = 09<br/>/PN = 10<br/>/PN = 11<br/>/PN = 12<br/>/PN = 13<br/>/PN = 14</pre>                                                                                                                                                            | /PN = 02 |     |            |      |      |         |    |

| /PN = 05       a[0] a[1] a[2]         /PN = 06       a[3] a[4] a[5] a[6]         /PN = 07       a[3] a[4] a[5] a[6]         /PN = 08       a[7] a[8] a[9]         /PN = 09       a[7] a[8] a[9]         /PN = 10       a[7] a[8] a[9]         /PN = 11       a[7] a[8] a[9]         /PN = 12       a[7] a[8] a[9]         /PN = 13       a[7] a[8] a[9] | /PN = 03 |     |            |      |      |         |    |

| /PN = 06         a[0]   a[1]   a[2]         /PN = 07       a[3]   a[4]   a[5]   a[6]         /PN = 08       a[7]   a[8]   a[9]         /PN = 09                                                                                                                                                                                                         | /PN = 04 |     |            |      |      |         |    |

| /PN = 07       a[3] a[4] a[5] a[6]         /PN = 08       a[7] a[8] a[9]         /PN = 09                                                                                                                                                                                                                                                               | /PN = 05 |     |            |      |      |         |    |

| /PN = 08 a[7] a[8] a[9]<br>/PN = 09<br>/PN = 10<br>/PN = 11<br>/PN = 12<br>/PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                                                                                                             | /PN = 06 |     | 1          | a[0] | a[   | 1] ¦ a[ | 2] |

| /PN = 09<br>/PN = 10<br>/PN = 11<br>/PN = 12<br>/PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                                                                                                                                        | /PN = 07 | a[3 | 3] [       | a[4] | a[   | 5] ¦ a[ | 6] |

| /PN = 10<br>/PN = 11<br>/PN = 12<br>/PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                                                                                                                                                    | /PN = 08 | a[7 | <u>]</u> [ | a[8] | a[   | 9]      |    |

| /PN = 11<br>/PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                                                                                                                                                                            | /PN = 09 |     |            |      |      |         |    |

| /PN = 12<br>/PN = 13<br>/PN = 14                                                                                                                                                                                                                                                                                                                        | /PN = 10 |     |            |      |      |         |    |

| /PN = 13<br>/PN = 14                                                                                                                                                                                                                                                                                                                                    | /PN = 11 |     |            |      |      |         |    |

| /PN = 14                                                                                                                                                                                                                                                                                                                                                | /PN = 12 |     |            |      |      |         |    |

|                                                                                                                                                                                                                                                                                                                                                         | /PN = 13 |     |            |      |      |         |    |

| /PN = 15                                                                                                                                                                                                                                                                                                                                                | /PN = 14 |     |            |      |      |         |    |

|                                                                                                                                                                                                                                                                                                                                                         | /PN = 15 |     |            |      |      |         |    |

Figure 19.2: Example: An Array In A Tiny Address Space

### Example: Accessing An Array

- TLB hit rate = 70%

- Sidenote:

- Caching is a fundamental performance technique used throughout computer systems to make "the common case" fast.

- Take advantage of locality (temporal and spatial)

| 0        | 0   | 04     | -    | fset<br>)8 | 12     | 1    | 6 |

|----------|-----|--------|------|------------|--------|------|---|

| -        | 0   | 04     |      | 0          | 12     |      | 0 |

| VPN = 00 |     |        |      |            |        |      |   |

| VPN = 01 |     |        |      |            |        |      |   |

| VPN = 02 |     |        |      |            |        |      |   |

| VPN = 03 |     |        |      |            |        |      |   |

| VPN = 04 |     |        |      |            |        |      |   |

| VPN = 05 |     |        |      |            |        |      |   |

| VPN = 06 |     |        | a[0] | a[1        | []   a | a[2] |   |

| VPN = 07 | a[3 | 8]   8 | a[4] | a[t        | 5]   8 | a[6] |   |

| VPN = 08 | a[7 | '] [ i | a[8] | a[         | 9]     |      |   |

| VPN = 09 |     |        |      |            |        |      |   |

| VPN = 10 |     |        |      |            |        |      |   |

| VPN = 11 |     |        |      |            |        |      |   |

| VPN = 12 |     |        |      |            |        |      |   |

| VPN = 13 |     |        |      |            |        |      |   |

| VPN = 14 |     |        |      |            |        |      |   |

| VPN = 15 |     |        |      |            |        |      |   |

Figure 19.2: Example: An Array In A Tiny Address Space

## Who Handles The TLB Miss?

- Is it the OS or hardware?

- Hardware Approach

- Hardware must know exactly where the page tables are located.

- On a miss, hardware walks the page table to update the TLB.

- OS Approach

- On a miss, hardware raises privilege level to kernel mode and jumps to a trap handler that will update the TLB through privileged instructions.

- Must ensure not to generate an infinite loop of TLB misses.

- More flexible and hardware is simple

### Who Handles The TLB Miss?

```

1 VPN = (VirtualAddress & VPN_MASK) >> SHIFT

2 (Success, TlbEntry) = TLB_Lookup(VPN)

if (Success == True) // TLB Hit

3

if (CanAccess(TlbEntry.ProtectBits) == True)

4

Offset = VirtualAddress & OFFSET_MASK

5

PhysAddr = (TlbEntry.PFN << SHIFT) | Offset

6

Register = AccessMemory (PhysAddr)

7

else

8

RaiseException (PROTECTION_FAULT)

9

// TLB Miss

else

10

RaiseException (TLB_MISS)

11

```

Figure 19.3: TLB Control Flow Algorithm (OS Handled)

## **TLB Contents: What's In There?**

- Typically, a TLB might have 32, 64, or 128 entries and be fully associative.

- TLB entry might look like this:

- VPN | PFN | other bits

- Must have VPN because it could be anywhere in the cache.

- Other bits are valid, protection, dirty bit, etc.

## **TLB Issue: Context Switches**

- TLB contents is only valid for the current running process. On a context switch, it becomes invalid. We must be careful.

- For example, if we have process P1 running.

- P1 might have a mapping of VPN 10 -> PFN 100

- Now P1 is context switched out for P2.

- P2 might have a mapping of VPN 10 -> PFN 170 VPN | PFN | valid | prot

| VPN | PFN | valid | prot |

|-----|-----|-------|------|

| 10  | 100 | 1     | rwx  |

|     |     | 0     |      |

| 10  | 170 | 1     | rwx  |

| —   |     | 0     |      |

## **TLB Issue: Context Switches**

- How do we solve this issue?

- Obvious simple approach...flush the TLB on context switch.

- Software approach, perhaps an instruction to flush the TLB.

- Hardware approach, perhaps flush when the page-table base register changes.

- This works but if we context switch often, we may have a high TLB miss rate.

- Some systems add hardware support to share the TLB with an address space identifier.

- Hardware must also know which process is running.

| VPN | PFN | valid | prot | ASID |

|-----|-----|-------|------|------|

| 10  | 100 | 1     | rwx  | 1    |

|     | _   | 0     |      |      |

| 10  | 170 | 1     | rwx  | 2    |

|     |     | 0     |      |      |

## **TLB Issue: Context Switches**

• In the case of sharing pages, maybe our TLB looks like this.

| VPN | PFN | valid | prot | ASID |

|-----|-----|-------|------|------|

| 10  | 101 | 1     | r-x  | 1    |

|     | —   | 0     | —    |      |

| 50  | 101 | 1     | r-x  | 2    |

| _   |     | 0     | —    |      |

## **Issue: Replacement Policy**

- Must consider how we do cache replacement when the cache is full.

- Look at this in more detail in the swapping pages chapters but we might use:

- Least Recently Used (LRU)

- Random: Works better in some edge cases like looping over n + 1 pages

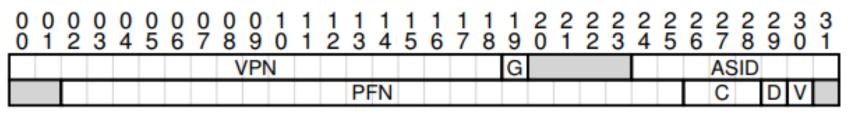

# A Real TLB Entry (MIPS R4000)

- 32-bit address space with 4KB pages.

- 20-bit VPN and 12-bit offset

- TLB is only 19-bit VPN because user addresses are limited to half the address space. Kernel reserves the other half.

- VPN translates to up to 24-bit PFNs for a max of 64GB of RAM

- Global bit (G) to ignore ASID

- 8-bit ASID (What if running more than 256 processes?)

Figure 19.4: A MIPS TLB Entry

# A Real TLB Entry (MIPS R4000)

- MIPS TLB usually have 32 or 64 entries with a few reserved for the OS.

- A "wired" register can be set by the OS to reserve slots in the TLB.

- MIPS TLB is software managed thus the OS uses specific instructions to manipulate the cache.

Figure 19.4: A MIPS TLB Entry